Detailed explanation of MOS tube working principle diagram

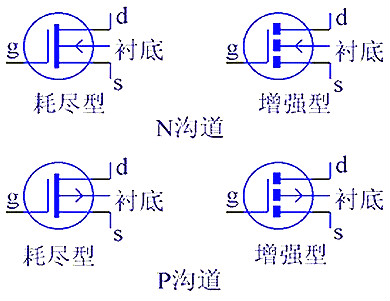

MOS transistor is one kind of FET (the other is JFET), which can be manufactured into enhanced or depleted type. There are four types of p-channel or n-channel, but only enhanced n-channel MOS transistor and enhanced p-channel MOS transistor are actually applied. Therefore, NMOS or PMOS are usually referred to.

NMOS is commonly used for these two enhanced MOS transistors. The reason is that the on resistance is small and easy to manufacture. Therefore, NMOS is generally used in switching power supply and motor drive applications. In the following introduction, NMOS is mainly used.

There is parasitic capacitance between the three pins of MOS tube, which is not what we need, but due to the limitation of manufacturing process. The existence of parasitic capacitance makes it more troublesome to design or select the driving circuit, but there is no way to avoid it. It will be introduced in detail later.

It can be seen from the working principle diagram of MOS tube that there is a parasitic diode between the drain and the source. This is called a body diode. This diode is very important in driving inductive loads (such as motors). By the way, bulk diodes exist only in a single MOS tube, which is usually not found in an integrated circuit chip.

The working principle of MOS tube detailed explanation of power switch circuit

This is the core of the device. Before introducing the working principle of this part, briefly explain the working principle diagram of MOS.

It generally has depletion type and enhancement type. Enhanced MOS is used in this paper

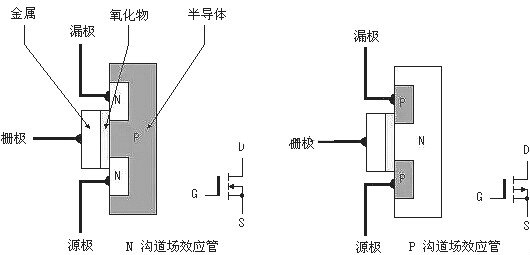

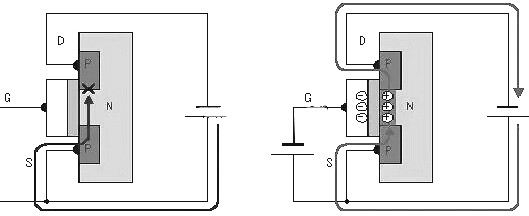

See the working principle diagram of MOS tube for its internal structure. It can be divided into NPN type and PNP type. NPN type is usually called n-channel type, and PNP type is also called p-channel type. As can be seen from the figure, the source and drain of n-channel FET are connected to n-type semiconductor, and the source and drain of p-channel FET are connected to p-type semiconductor. We know that the general triode is controlled by the input current and the output current. However, for FET, its output current is controlled by the input voltage (or electric field). It can be considered that the input current is very small or there is no input current, which makes the device have high input impedance. At the same time, this is also the reason why we call it FET.

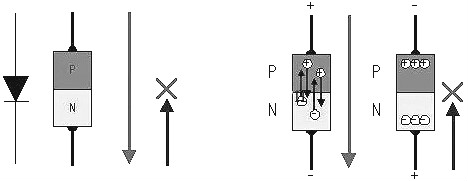

In order to explain the working principle of MOS transistor, we first understand the working process of diode with only one p-n junction. As shown in the figure, we know that when the diode is applied with a forward voltage (P terminal is connected to the positive pole and N terminal is connected to the negative pole), the diode is turned on and the PN junction has current. This is because when the p-type semiconductor terminal is at a positive voltage, the negative electrons in the n-type semiconductor are attracted and flow to the p-type semiconductor terminal with a positive voltage, while the positive electrons in the p-type semiconductor terminal move towards the n-type semiconductor terminal to form an on current. Similarly, when the diode is applied with a reverse voltage (p-terminal is connected to the negative electrode and N-terminal is connected to the positive electrode), there is a negative voltage at the p-type semiconductor terminal, the positive electrons are gathered at the p-type semiconductor terminal, the negative electrons are gathered at the n-type semiconductor terminal, the electrons do not move, there is no current through its PN junction, and the diode is cut off.

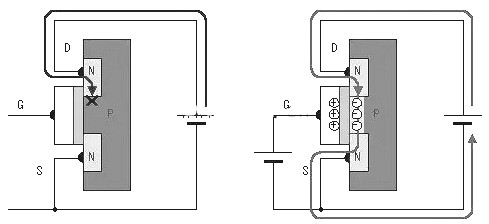

For MOS transistor (see Figure), when there is no voltage at the grid, it can be seen from the previous analysis that there will be no current flow between the source and drain. At this time, the MOS transistor is in the cut-off state (figure a). When a positive voltage is applied to the n-channel MOS transistor.

When the MOS tube is on the gate, due to the action of the electric field, the negative electrons of the source and drain of the n-type semiconductor are attracted and flow to the gate. However, due to the barrier of the oxide film, the electrons gather in the p-type semiconductor between the two n-channels (see Fig. B), so as to form a current and conduct between the source and drain. We can also imagine that there is a channel between two n-type semiconductors. The establishment of gate voltage is equivalent to building a bridge between them. The size of the bridge is determined by the size of gate voltage. Figure shows the MOS transistor of p-channel.

MOS tube working principle diagram working process, its working principle is similar, and it will not be repeated here.

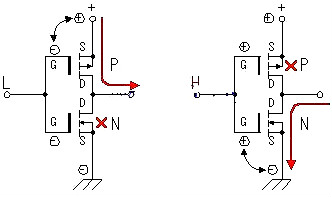

The working process of the application circuit composed of C-MOS FET (enhanced MOS transistor) is briefly described below (see Figure). The circuit combines an enhanced p-channel MOS transistor and an enhanced n-channel MOS FET. When the input end is at low level, the p-channel MOS tube is turned on, and the output end is connected with the positive pole of the power supply. When the input is at high level, the n-channel MOS FET is turned on, and the output is connected to the power ground. In this circuit, p-channel MOS FET and n-channel MOS FET always work in the opposite state, and their phase input and output are opposite. In this way, we can get a larger current output. At the same time, due to the influence of leakage current, the gate voltage is not up to 0V. Usually, when the gate voltage is less than 1 to 2V, the MOS FET is turned off. The off voltage of different FET is slightly different. Because of this, the circuit will not cause a power short circuit because the two tubes are connected at the same time.

From the above analysis, we can draw the working process of MOS transistor circuit in MOS transistor working principle diagram (see Figure). The working principle is the same as that described above.

MOS transistor application circuit

The most remarkable characteristic of MOS transistor is its good switching characteristics, so it is widely used in circuits that need electronic switches, such as switching power supply and motor drive, as well as lighting dimming.

There are several special requirements for MOS driver:

1. Low voltage application

When 5V power supply is used, if the traditional MOS transistor working principle diagram totem column structure is used, because the be of the triode has a voltage drop of about 0.7V, the actual final voltage applied to the gate is only 4.3v. At this time, there is a certain risk when we choose MOS transistor with nominal gate voltage of 4.5V.

The same problem also occurs when 3V or other low-voltage power supplies are used.

2. Wide voltage application

The input voltage is not a fixed value, it will change with time or other factors. This change causes the driving voltage supplied by the PWM circuit to the MOS transistor to be unstable.

In order to make MOS transistors safe under high gate voltage, many MOS transistors have built-in voltage regulators to forcibly limit the amplitude of gate voltage. In this case, when the supplied driving voltage exceeds the voltage of the regulator, it will cause large static power consumption.

At the same time, if the gate voltage is simply reduced by the principle of resistance voltage division, the MOS transistor will work well when the input voltage is relatively high, and the gate voltage is insufficient when the input voltage is reduced, resulting in incomplete conduction, thus increasing power consumption.

3. Dual voltage application

In some control circuits, the logic part uses a typical 5V or 3.3V digital voltage, while the power part uses a voltage of 12V or even higher. The two voltages are connected by common ground.

This puts forward a requirement. A circuit needs to be used to enable the low-voltage side to effectively control the MOS tube on the high-voltage side. At the same time, the MOS tube on the high-voltage side will also face the problems mentioned in 1 and 2.

In these three cases, the totem pole structure can not meet the output requirements, and many ready-made MOS drive ICs do not seem to include the structure of gate voltage limitation.

So I designed a relatively general circuit to meet these three needs.

The working principle diagram of MOS tube is as follows:

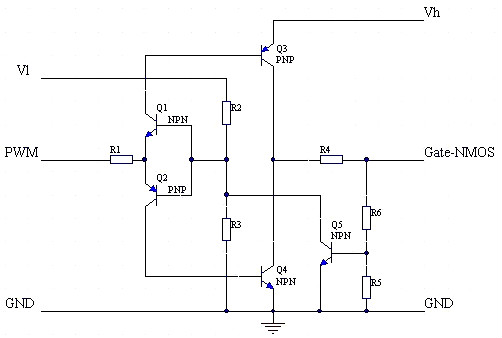

Driving circuit for NMOS

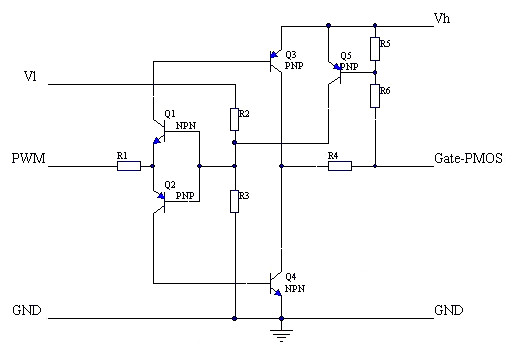

Driving circuit for PMOS

NMOS driver circuit to do a simple analysis

VL and VH are low-end and high-end power supplies respectively. The two voltages can be the same, but VL should not exceed VH.

Q1 and Q2 form an inverted totem pole to realize isolation and ensure that the two drive tubes Q3 and Q4 will not be connected at the same time.

R2 and R3 provide PWM voltage reference. By changing this reference, the circuit can work at the position where the PWM signal waveform is relatively steep.

Q3 and Q4 are used to provide driving current. When conducting, Q3 and Q4 have the lowest voltage drop of VCE relative to VH and GND. This voltage drop is usually only about 0.3V, which is much lower than VCE of 0.7V.

R5 and R6 are feedback resistors used to sample the gate voltage. The sampled voltage generates a strong negative feedback to the bases of Q1 and Q2 through Q5, so as to limit the gate voltage to a limited value. This value can be adjusted by R5 and R6.

Finally, R1 provides the base current limit for Q3 and Q4, and R4 provides the gate current limit for MOS transistors, that is, the ice limit for Q3 and Q4. If necessary, the accelerating capacitor can be connected in parallel on R4.

This circuit provides the following characteristics:

1. Drive high-end MOS tube with low-end voltage and PWM.

2. The MOS transistor with high gate voltage demand is driven by a small amplitude PWM signal.

3. Peak limit of gate voltage

4. Input and output current limits

5. Low power consumption can be achieved by using appropriate resistors.

6. The PWM signal is inverted. NMOS does not need this feature, which can be solved by pre positioning an inverter.

When designing portable devices and wireless products, improving product performance and prolonging battery working time are two problems that designers need to face. DC-DC converter has the advantages of high efficiency, large output current and small static current. It is very suitable for supplying power to portable devices.

Main development trends of DC-DC converter design technology:

(1) High frequency technology: with the increase of switching frequency, the volume of switching converter is reduced, the power density is greatly improved, and the dynamic response is improved. The switching frequency of low-power DC-DC converter will rise to MHz.

(2) Low output voltage technology: with the continuous development of semiconductor manufacturing technology, the working voltage of microprocessors and portable electronic devices is getting lower and lower, which requires that the future DC-DC converter can provide low output voltage to meet the requirements of microprocessors and portable electronic devices.

The development of these technologies puts forward higher requirements for the design of power chip circuit. Firstly, with the continuous improvement of switching frequency, high requirements are put forward for the performance of switching elements. At the same time, corresponding switching element driving circuit must be provided to ensure the normal operation of switching elements at switching frequency up to MHz. Secondly, for battery powered portable electronic devices, the working voltage of the circuit is low (taking lithium battery as an example, the working voltage is 2.5 ~ 3.6V). Therefore, the working voltage of the power chip is low.

MOS transistor has very low on resistance and low energy consumption. MOS transistor is often used as power switch in popular high-efficiency DC-DC chips. However, due to the large parasitic capacitance of MOS transistors, the gate capacitance of NMOS switching transistors is generally as high as tens of picofarms. This puts forward higher requirements for the design of switch driver circuit of high working frequency DC-DC converter.

In low voltage ULSI design, there are many CMOS and BiCMOS logic circuits with bootstrap boost structure and driving circuits as large capacitive loads. These circuits can work normally under the power supply condition of less than 1V, and can work under the condition of load capacitance of 1 ~ 2pF, and the frequency can reach tens of megahertz or even hundreds of megahertz. In this paper, a bootstrap boost circuit is used to design a drive circuit with large load capacitance, which is suitable for low voltage and high switching frequency boost DC-DC converter. The circuit is designed based on Samsung ahp615 BiCMOS process and verified by HSPICE simulation. When the power supply voltage is 1.5V and the load capacitance is 60pf, the working frequency can reach more than 5MHz.

MOS switch tube loss

Whether NMOS or PMOS, there is an on resistance after conduction, so the current will consume energy on this resistance. This part of the consumed energy is called on loss. Selecting MOS transistor with low on resistance will reduce on loss. At present, the on resistance of low-power MOS tubes is generally about tens of milliohms, and there are also a few milliohms.

MOS must not be completed in an instant when it is on and off. The voltage at both ends of MOS has a falling process, and the current flowing has a rising process. During this period, the loss of MOS transistor is the product of voltage and current, which is called switching loss. Generally, the switching loss is much greater than the conduction loss, and the faster the switching frequency, the greater the loss.

The product of voltage and current at the moment of conduction is very large, resulting in great loss. Shortening the switching time can reduce the loss of each conduction; Reducing the switching frequency can reduce the switching times per unit time. Both methods can reduce the switching loss.

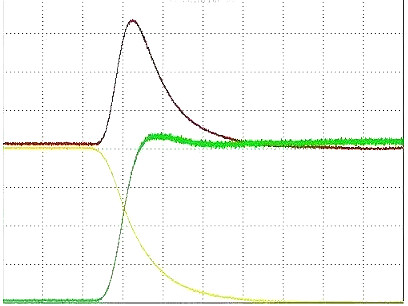

The figure above shows the working principle diagram of MOS tube and the waveform when it is turned on. It can be seen that the product of voltage and current at the moment of conduction is very large, resulting in great loss. Reducing the switching time can reduce the loss of each conduction; Reducing the switching frequency can reduce the switching times per unit time. Both methods can reduce the switching loss.

Cause analysis of MOS tube heating

In the hardware development of a routing product, one of them is that customers need non-standard Poe power supply. The output Poe power supply voltage is 12 / 24 / 30 / 48V switching, and the maximum output power is designed to be 24W. The circuit adopts flyback power supply scheme (power chip mp3910, scheme provided by the chip manufacturer). When debugging this part of the circuit, MOS transistor (NMOS, sud50n06) is seriously heated, The output voltage is normal when it is not loaded. When it is loaded (50% at the beginning), the MOS tube is seriously heated and the output voltage is pulled down. No matter which voltage is output, the output is only about 9V, and the voltage stabilizing value of TLV431 is only about 1V (the normally selected model VREF = 2.5V). At the beginning, I always feel that the problem is in TLV431, Later, when the board was changed, it was found that the voltage could be stabilized normally (there should be a problem with the transformer and MOS tube of the previous board, but it was not verified). However, the MOS tube was very hot and would smoke in less than ten seconds. Later, after communicating with the FAE of the chip scheme, it was found that the current limiting resistance between the gate pin of the driving MOS tube of msp3910 and the MOS tube was made of the wrong material, The working principle diagram of MOS tube is 4.99 Ω, but the actual use is 4.99k. After replacing the resistance, the normal voltage can be output, and the MOS tube will not be very hot.

The following is the idea to solve the problem:

1、 Observe the g-pole waveform of the MOS tube used with an oscilloscope. As shown in Figure 1, the rise time is close to 1.32us and the fall time is close to < 160ns (measured 50ns). Then look at the requirements for the rising and falling edge of MOS drive in the manual shown in Figure 2. The rise time is less than 35ns and the fall time is less than 80ns. It can be concluded that the MOS tube works in a linear state due to the long rise time, In the non switching state (see summary I), the MOS tube is turned on for too long, which directly leads to serious heating of the MOS tube.

2、 Solution: replace the drive current limiting resistor (RG in Figure 2). Since there was no 4.99 ohm resistor in hand at that time, after replacing it with a 22 ohm resistor, the g-pole waveform is shown in Figure 3. Ton and toff are close to the time required in Figure 2. When the MOS tube is 24V, the load is 27 ohm, the output power is 21.3w, the output voltage is normal, and the MOS tube is basically not heated.

Summary I: summary of MOS tube heating causes

1. The problem of circuit design is to make MOS tube work in linear working state, not in switching state. This is also a cause of MOS tube heating. If n-MOS is used as a switch, the g-level voltage must be several V higher than the power supply before it can be fully turned on, and p-Mos is the opposite. If it is not fully opened and the voltage drop is too large, the success rate is consumed, the equivalent DC impedance is relatively large, and the voltage drop increases, so the U * I also increases, and the loss means heating. This is the most taboo mistake in designing circuits( Although the problem of this product test is not in the circuit design, the BOM error is often more difficult to analyze than the design error)

2. The frequency is too high, mainly due to the excessive pursuit of volume sometimes, resulting in the increase of frequency, the loss on MOS tube increases, so the heating also increases;

3. There is not enough heat dissipation design, the current is too high, and the nominal current value of MOS tube generally needs good heat dissipation. Therefore, if the ID is less than the maximum current, there may be serious heating, and sufficient auxiliary fins are required;

4. The selection of MOS tube is wrong, the power judgment is wrong, and the internal resistance of MOS tube is not fully considered, resulting in the increase of switching impedance.

Summary 2: MOS transistor working state analysis

There are four working states of MOS tube: on process, on state, off process and off state;

Main losses of MOS tube: switching loss, conduction loss, cut-off loss, avalanche energy loss and switching loss

The loss is often greater than the latter;

Main damage causes of MOS tube: overcurrent (continuous high current or instantaneous high current), overvoltage (D-S and G-S are broken down), static electricity (I think it can belong to overvoltage);

Summary 3: MOS transistor working process analysis

The working process of MOS transistor is very complex and there are many variables inside. In short, slow switching is not easy to cause Miller oscillation (Miller capacitor, Miller effect, etc. are introduced in detail), but the switching loss will increase and the heat will be large; The switching speed is fast and the loss will be reduced, but Miller's shock is very strong, which will increase the loss. The requirements for driving circuit wiring and main circuit wiring are very high. The final goal is to find a balance point. Generally, the opening process does not exceed 1US;

Summary 4: important parameters and type selection of MOS transistor

Qgs: when the grid is charged from 0V to the corresponding current Miller platform, the total charge is charged. At this time, the CGS is charged (equivalent to CISS, input capacitance);

QGD: total charging charge of the whole Miller platform (not necessarily larger than Qgs, only Miller platform);

QG: total charge, including Qgs, QGD and others;

The unit of the above three parameters is NC (nano Library), which is generally several NC to tens of NC;

RDS (on): turn on the internal resistance. Under certain withstand voltage, the smaller the loss;

General selection rules: pipes with smaller Qgs, QGD and QG and smaller RDS (on).